Granite River Labs, GRL

Robert Yang

DisplayPort 1.4(DP1.4)は、市場最高の画質を誇る最新のディスプレイ伝送技術です。 DP1.4は優れた伝送性能を持ち、最大7680x4320 @60Hz(8K)の解像度で画像を出力することができます。DisplayPortの高速信号伝送は、一方向ので、Source(送信側:コンピューターなど)からSink(受信側:ディスプレイ装置など)に高速信号を出力し、高品質な表示を行います。

DP1.4 PHY 概要

この記事では、DP1.4の物理層テストについて、以下のの2つのパートに分けてわかりやすく説明します。

- トランスミッタ(TX)

- レシーバ(RX)

DP1.4 TXイコライザ

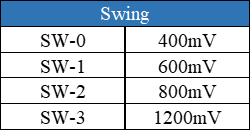

PHY テストを紹介する前に、まず DisplayPort で使用されるイコライザについて簡単に説明します。 DP1.4 インターフェースは、かなり高速で信号を伝送するため、伝送中の損失が多くなります。 基板上の回路や、接続されたケーブルが損失の原因となる可能性があります。 Sinkに伝送される信号が損失により識別できなくなることを避けるため、DisplayPortのTx送信端とRx受信端に異なるEQ(Enhancement Mode)が設けられています。 スイングは出力信号の振幅を調整します。 プリエンファシスは伝送路で減衰する高周波成分を補正するため、連続信号の最初のビットの振幅を調整します。 プリエンファシスレベルが高いほど、エンハンス比(最初のビット振幅/後続の連続ビット振幅)が大きくなります。

表1 トランスミッタEQ

DP1.4 RXイコライザ

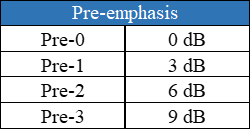

DP1.4 の Rx受信端では、高速信号を復元するために、DFE と 10 種類の CTLE が設定されています。 CTLE は伝達関数で、信号の高周波成分を増幅し、低周波成分を減衰させ、高周波と低周波のバランスをとることで、きれいなアイダイヤグラムを得ます。

図1 DP1.4 CTLE(Rx EQ): HBR3

1.DP1.4 トランスミッタ(Tx) PHY

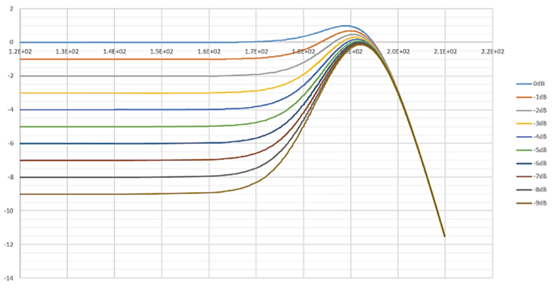

Txの試験では、DUT(Source)をReference Sinkと接続し、DUTを試験モードに設定します。 テストパターン、スイング/プリエンファシスレベル、SSC On/Offなど、出力信号の種類やパラメータの異なった信号をDUTから出力します。

表2 DP1.4 Tx テストパターン

表2 DP1.4 Tx テストパターン

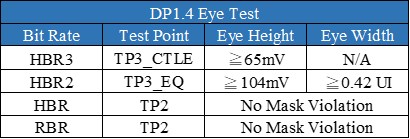

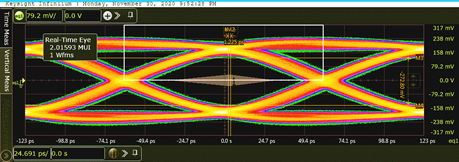

1-1アイダイアグラムテスト

アイダイアグラムテストは、信号品質を確認するための最も基本的な方法です。 一般的には、信号のアイダイアグラムのアイ幅とアイハイトを観察し、アイマスクに触れているかどうかで、Sourceの出力信号がSinkで認識できるかどうかを確認するものです。 DP1.4の信号速度の違いによるアイハイトとアイ幅の仕様を表3に示します。また、HBR3のアイダイアグラム例を図2に示します。

表3 DP1.4 アイテスト規格値

図2 DP1.4 アイダイアグラム例

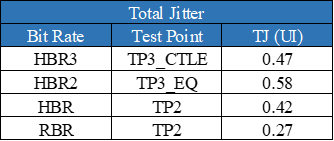

1-2ジッタテスト

ジッタは伝送品質に影響を与える最も重要な要因であり,デターミニスティックジッタ(DJ)とランダムジッタ(RJ)に分類され,その中でDJはSJ,DDJ(ISI),BUJなどに分けられます。 DP試験においては、以下のようなジッタ解析が必要です。

•ランダムジッター

熱雑音や環境などの不確定な要因によって発生することが多い。

•SJ(Sine Jitter)

基板上の発振器や電源などの干渉源によって発生する周期的なジッター。

•ISI(Inter Symbol Interference:符号間干渉)

通常、信号経路が長いほど(高周波ロスが多いほど)ISI干渉は大きい。

•トータル・ジッター(TJ)

上記のジッター成分の総和

DP1.4におけるTotal Jitterの仕様を以下に示します。

表4 DP1.4 ジッタテスト 規格値

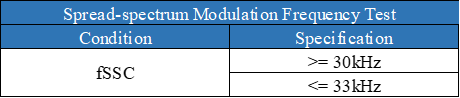

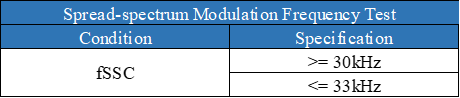

1-3スペクトラム拡散(SSC)テスト試

DisplayPortでは、伝送信号が特定の周波数にエネルギーが集中することで、他に干渉を与えないようData Rateの周波数を分散するSSC技術が採用されています。 SSC を試験する場合、SSC の周波数と変調度を別々に測定します。CTS での規格値を以下に示します。

表5 DP1.4 SSCテスト規格値

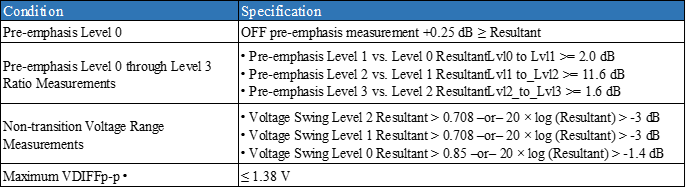

1-4 VTXテスト(スイング/プリエンファシス テスト)

出力信号のSwingとPre-emphasisの比率が十分であるかどうかを確認するための試験です。

テストでは,PLTPAT (pre-emphasis level test pattern)を使用します。 オシロスコープでキャプチャされた出力信号から,Transition Bit と Non-Transition Bit の比が計算されます。

表6 スイング/プリエンファシス レベルテスト 規格値

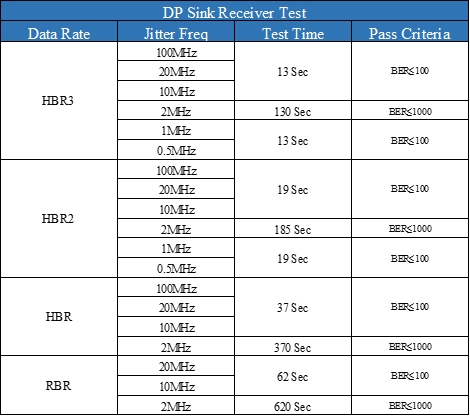

2.DP1.4 レシーバ(Rx) PHY

Rx側のテストは、リファレンスソースをDUT(Sink)に接続し、DUTをテストモー ドに移行させます。 その後、BERT(ビットエラーテスタ、信号発生器)を使用して、規定のノイズ信号(ランダムジッタ、サインジッタ、ISI、クロストークを含む)をSinkに入力し、RxのICが正確に受信できることを確認します。

Q:受信側のICが入力信号を正確に解釈しているかどうかを確認する方法は?

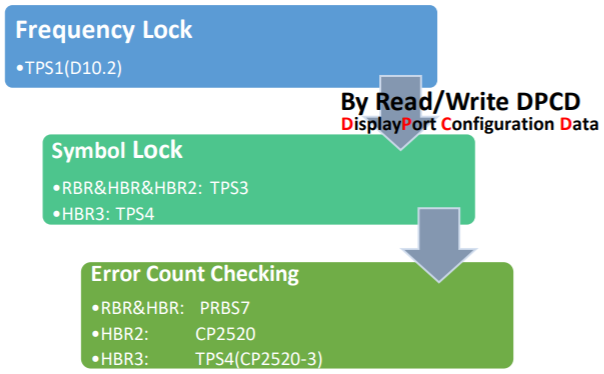

画面上で明るい線が点滅しているかどうかは、肉眼で観察することができます。しかし、高速信号はクリアに判別できません。 また、DPの設計上、USBインタフェースにあるLoopbackモードは存在しません。 そこで、テスト時にはDPCDを使用して、Sinkでのリードエラー発生の有無を確認することにしています。 SinkのICに内蔵された、DPCD(DisplayPort Configuration Data)レジスタは、AUXチャネルを通じて、読み書きが可能で、Sinkの仕様(DPバージョン、最大速度、サポートチャネル数などを呼び出すことができます。 また、エラー検出にもDPCDを利用することができます。

テスト際には、Sinkに入力テストパターンをDPCDを書き込むことによって伝えます。 シンクは入力信号と期待されるテストパターンを比較し、矛盾したビットを発見した場合,エラーカウントのレジスタにエラーの数が記入されます。

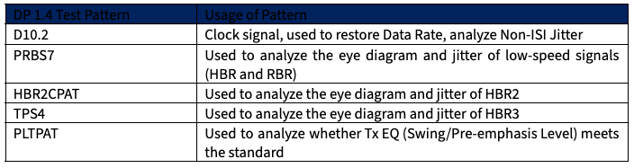

シンク PHY テストには、3 つのステージがあります。 各ステージごとに、BERT からり異なるパターンを出力します(図 3)。

回歸正題,在DPCD的某個特定位址,會記錄Sink端此時收到的Error,即我們在測試時會透過寫入DPCD 的方式,告訴Sink此時要輸入何種測試Pattern,而當Sink比對輸入訊號後發現,有不一致的位元時便會在Error Count 的Register 填入Error的數量。

進行Sink PHY測試會有三個步驟,在不同的階段需要由BERT端輸出不同的Pattern (圖三)。

- 周波数ロック:クロックパターンを出力し、周波数ロックされるかを確認。

- シンボルロック:テストパターンを出力し、EQの調整、シンボルロックの確認。

- エラーカウント:テストパターンを比較し、エラー量を記録する。

CTSでは、Sinkの "Error Count "を一定時間観測し、試験結果のPass/Failを判断します。(表7)

図3 DP1.4 Sink PHYテストプロセス

表7 DP1.4 Sink レシーバテストスピード/規格値

参考文献

- VESA DisplayPort (DP) Standard Version 1.4a 19 April 2018: https://vesa.org/

- VESA DisplayPort v1.4a PHY Layer Compliance Test Specification, Rev1.1, 05 June 2020: https://vesa.org/

文章下載

著者

Robert Yang テストエンジニア GRL-Taiwan

ロバートは4年間のテスト経験を持ち、DisplayPort™、Thunderbolt、HDMI®、USBなどのテストに精通しています。

現在、GRL(台湾)で主に互換性試験を担当しており、お客様の問題解決、認証取得の支援を行っています。