DDR 測試

DDR 介面總覽

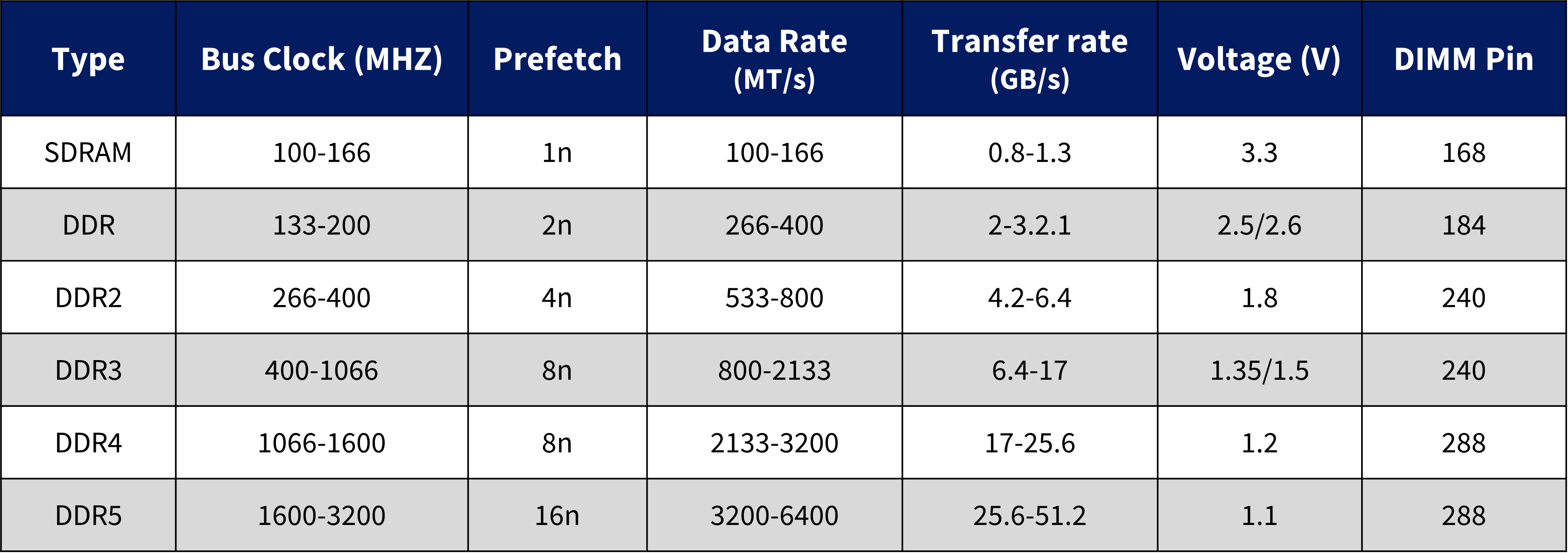

Double Data Rate,DDR 為記憶體傳輸標準,用名稱直譯也能幫助理解:每個時間脈衝週期(clock cycle)有雙倍資料傳輸。 記憶體規格,從初期的DDR、DDR2、DDR3、DDR4演進到 DDR5。 不同的DDR 標準,會有不同的針腳、傳輸速度、功耗等。

JEDEC 協會

全稱為JEDEC Solid State Technology Association,固態技術協會,成立於1958年,是微電子產業的主導標準機構,且JEDEC不隸屬於任何一個國家或政府實體。JEDEC主要任務在標準化固態儲存器(SSD)、DRAM、快閃記憶卡(Flash card)、無線射頻辨識(RFID)等產品的生產、測試、功能定義。更多訊息請參考 https://www.jedec.org

DDR 測試規範

由於DDR每種版本的spec都不同。請輸入JEDEC帳號 & 密碼後到以下網址查詢:

https://www.jedec.org/standards-documents

測試專區

GRL可以測試的DDR產品類型及範例

技術資源

- 技術文章:DDR Overview

DDR 測試流程

DRAM 組件上必須安裝中介層以便探測 DDR 訊號。 如果能提供 S 參數,則中介層可以解嵌。 GRL 所提供的額外收費服務包括選擇和安裝 DDR 中階層。

客戶需要提供的設備:

- 每款測試組件的精確 DQ(資料位元)、DQS(選通脈衝)和 A(位址位元)。

- 主機(Host)控制器系統

- 產生特定資料流的軟體工具,能夠以安裝了中介層的晶片顆粒為目標,在測試期間盡可能使用 DQ 和位址位。

DDR 數據流要求:

- DDR 僅使用隨機資料和不少於8個位元組的資料區塊進行寫入。 為了在突發傳輸中獲得更多的 b0 和 b1 以產生 DDR 眼圖,數據必須保持隨機性。 測試 DDR5則需要至少涵蓋200個時脈週期的資料流。

- DDR 只能讀取隨機資料和不少於8個位元組的資料區塊。 提供的腳本可以是對指定位置執行隨機寫入,然後開始無限突發讀取。

- 用於測試 JEDEC 規範的最佳資料流是 DDR 資料區塊的連續讀寫交替模式。

DDR 測試項目

DDR 2-3/LPDDR 2-3:

- 設定 1:DQ/DQS 讀取和寫入、CS# 和時鐘

- 設定 2:地址、CAS#、RAS# 和 WE#

DDR 5/DDR 4/LPDDR 4/LPDDR 4x:

- 差分配置:時脈#、DQS#、DQ-x 讀取和寫入、命令(位址-x 或 CS#)

- (可選項目)單端配置:時鐘和/或 DQS

LPDDR 5:

- 差分配置:Clock#、RDQS#、DQ-x 讀取和寫入以及 WCK#

- (可選項目)單端設定:Clock#、RDQS# 和/或 WCK#

- (選用項目)接收器物理層

如果想要控制測試成本,可以只在 DIMM 端執行寫入訊號的測試。 或僅在 Host 端進行讀取訊號的測試,或降低待測資料的選擇配置。

DDR 使用儀器

DDR 測試設備

- Keysight 或 Rohde & Schwarz RTP 16GHz 即時示波器

- 差分探頭

- DDR 合規測試自動軟體