Granite River Labs, GRL

Robert Yang 楊宗霖

DP1.4 為現行市面上最新、最高畫質的顯示傳輸技術,透過DP1.4 的傳輸規格,可以輸出到最高7680×4320 @60Hz(8K) 的解析度。DisplayPort的高速訊號為一種單向的傳輸技術,Source (發送端 – 如電腦) 會將高速訊號輸出到 Sink (接收端 – 如螢幕),以達到高畫質的顯示。

DP1.4 PHY Overview

本篇文章將深入淺出的帶大家探討DP1.4的物理層 (Physical Layer) 測試。

物理層的測試主要可分為:

- 傳送端 (Transmitter – Tx)

- 接收端 (Receiver – Rx)

DP1.4 Equalizer

在介紹以上兩種PHY的測試前,讀者可以先了解在DisplayPort上會使用到的Equalizer (等化器)。因為DP1.4為相當高速的訊號,訊號在傳輸時免不了有相當程度的損耗,損耗來源可能為電路板上的線路或是連接的Cable,為了避免這些損耗導致訊號傳送到Sink端時無法被辨識,DisplayPort在Tx 與 Rx端均設計了不同的加強方式(EQ):

1. DP1.4 Tx Equalizer

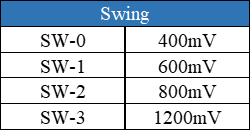

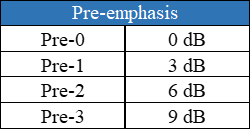

在傳送端,DP1.4 使用了不同等級的Swing/Pre-emphasis Level 來加強訊號:Swing 為調整輸出訊號振福,Pre-emphasis 則是對連續訊號的第一個Bit做預加強,越高的Pre-emphasis Level加強的比值(第一個Bit/後面連續Bit) 越大。

表 1:Transmitter EQ

2. DP1.4 Rx Equalizer

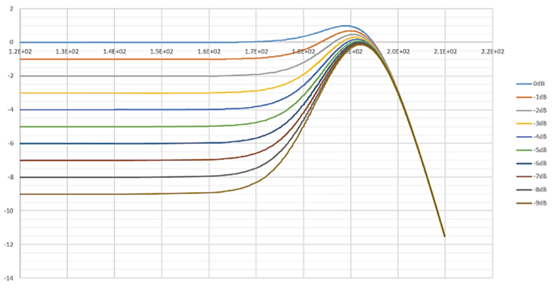

而在接收端方面,DP1.4 則設計了DFE以及10種不同的CTLE來對高速訊號做運算還原,CTLE為一種針對不同頻率的轉移函數,此轉移函數會將訊號的高頻成份放大,低頻成份衰減,來達到訊號高低頻的均衡,進而使接收端收到的眼圖更漂亮。

圖 1:DP1.4 CTLE (Rx EQ) for HBR3

接下來讓我們正式進入DP1.4 電性測試的介紹:

1. DP1.4 Transmitter (Tx) PHY

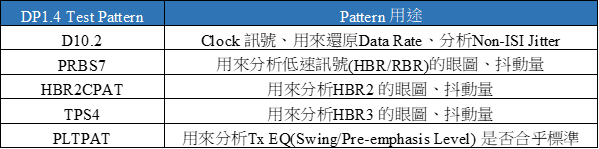

在Tx 訊號測試時,我們會透過Reference Sink 來與DUT (Source) 連接,誘使DUT進入測試模式,進而改變輸出的訊號的種類及參數,包括不同的測試Pattern,Swing/Pre-emphasis Level,SSC On/Off 等等。

表 2

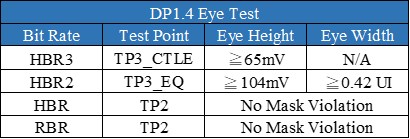

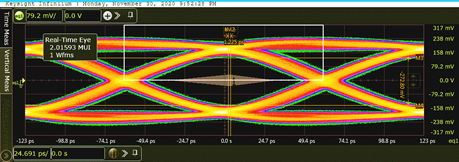

1.1 眼圖測試

眼圖測試為用來驗證訊號品質最基本的方法,一般來說,透過觀察訊號眼圖的眼寬及眼高,是否觸碰到Eye Mask,可以了解Source 產品所輸出的訊號是否足以被Sink所辯識。以下列出DP1.4 在不同速度的眼高、眼寬規範(表三),並以一HBR3 的眼圖為例子(圖二)。

表 3

圖 2

1.2 Jitter測試

Jitter(抖動) 為影響訊號品質的最主要原因,其成分又可劃分為Deterministic Jitter-DJ (確定性抖動)與Random Jitter-RJ(隨機抖動),其中DJ 又可區分為SJ、 DDJ(ISI) 、BUJ 等等成分而在DP 的測試中,需進行以下的Jitter分析:

• Random Jitter: 隨機抖動,常見的來源有熱干擾,環境等不確定的干擾。

• Sine Jitter(SJ): 週期性抖動,常見的有電路板上的震盪器,電源等干擾。

• ISI(Inter symbol interference): 通常訊號走過的路徑越長,此干擾越大。

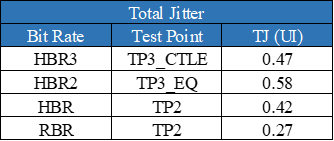

• Total Jitter(TJ): 以上所有Jitter成分加成,以下為4 Total Jitter 的規範:

表 4

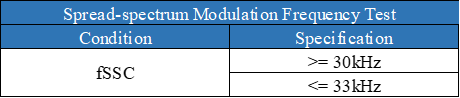

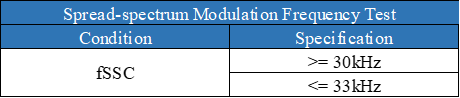

1.3 Spread-spectrum(SSC) 展頻測試

為了避免高速訊號集中在某個頻段而成為干擾源,DisplayPort 採用了SSC的展頻技術,將Data Rate 頻率打散。

在測試SSC時,會針對SSC的頻率以及大小分別進行量測,以下為CTS中規範的標準:

表 5

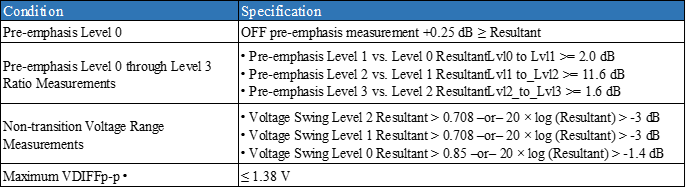

1.4 VTX 測試 (Swing/ Pre-emphasis Level Test)

此測試旨在驗證輸出的訊號Swing 與 Pre-emphasis加重的比例是否足夠,這裡使用的是PLTPAT (Pre-emphasis level test pattern),測試時,示波器會將訊號由時域轉換為頻域,並計算出Transition Bit (轉態位元)與Non-Transition Bit (非轉態位元) 的比值。

表 6

2. DP1.4 Receiver (Rx) PHY

對於接收端Rx 的測試,我們一樣會透過Reference Source 來與DUT (Sink) 溝通,誘使Sink進入測試模式。接著,我們會透過BERT (誤碼儀、訊號產生器) 將一段充滿雜訊的訊號 (包含Random Jitter, Sine Jitter, ISI, Crosstalk 等等成分) 輸入到Sink端,確保接收端的IC 仍可準確的判讀訊號的0與1準位。

Q:至於要如何確認接收端IC是否有準確判讀輸入的訊號呢?

肉眼辨認是一種方式,觀察畫面是否有亮線閃爍等。但這對高速訊號來說不夠明確,且在DP的設計也沒有USB介面的Loopback mode模式。故在進行測試時,我們會透過DPCD的讀取跟寫入,來判斷Sink端是否有訊號誤判的情形發生。

DPCD全名為DisplayPort Configuration Data,它儲存在Sink的 IC上,上面會宣告Sink的能力 (DP版本,最大速度,支援幾個通道等)。同時,也可以在上面寫入數值,以進行Source及Sink間的Link training 溝通。

回歸正題,在DPCD的某個特定位址,會記錄Sink端此時收到的Error,即我們在測試時會透過寫入DPCD 的方式,告訴Sink此時要輸入何種測試Pattern,而當Sink比對輸入訊號後發現,有不一致的位元時便會在Error Count 的Register 填入Error的數量。

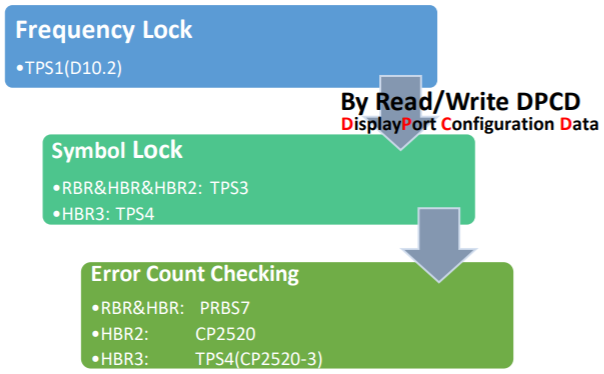

進行Sink PHY測試會有三個步驟,在不同的階段需要由BERT端輸出不同的Pattern (圖三)。

1. Frequency Lock : 此階段會進行傳輸速度、幾個Lane的比對。

2. Symbol Lock : 此階段會進行EQ 的調整,測試Pattern的Align。

3. Error count : 最後階段,進行Test Pattern 的比對,並記錄錯誤量。

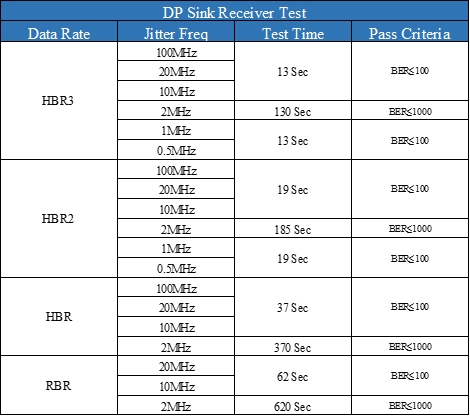

依照CTS,需在一定的時間內觀察Sink的”Error Count”來判斷測試結果為Pass或Fail (表七) 。

圖 3

表 7

參考文獻

- VESA DisplayPort (DP) Standard Version 1.4a 19 April 2018: https://vesa.org/

- VESA DisplayPort v1.4a PHY Layer Compliance Test Specification, Rev1.1, 05 June 2020: https://vesa.org/

文章下載

作者

GRL台灣測試工程師 楊宗霖 Robert Yang

具四年測試經驗,熟悉DisplayPort、Thunderbolt、HDMI、USB 等多種測試規範。目前負責GRL台灣相容性測試部門,樂於協助客戶的各種問題,以順利取得認證。

本文件中規格特性及其說明若有修改恕不另行通知。

發佈日期 2021/03/09 AN-210309-TW