Granite River Labs, GRL

藍婉甄 Nicole Lan

MIPI(行動產業處理器介面)由MIPI聯盟發起,全名為Mobile Industry Processor Interface,是為行動產業處理器所制定的開放標準。MIPI聯盟於2003年由美國德州儀器(TI)、意法半導體(ST)、芬蘭諾基亞(Nokia)以及英國ARM等公司共同成立。MIPI聯盟為開放的會員制組織,所有手機行業內的公司皆可加入,包含:手機設備製造商、系統供應商、軟體廠商、半導體廠商等公司。

MIPI聯盟主要目的在於推進手機內部硬體和軟體介面的標準化,提供了全面的規範組合,用於連接行動設備中的晶片組和外圍設備。手機製造商因而能使用這些規範來優化性能、簡化設計過程、降低開發成本、創造規模經濟並縮短產品的上市時間。

MIPI介面與多媒體類別

MIPI規範包含六種類型的介面:

- 物理層(Physical layer)

- 多媒體(Multimedia)

- 芯片到芯片/處理器間通信(Chip-to-chip/inter-processor communications)

- 設備控制和數據管理(Device control and data management)

- 系統除錯(System debugging)

- 軟體整合(Software integration)

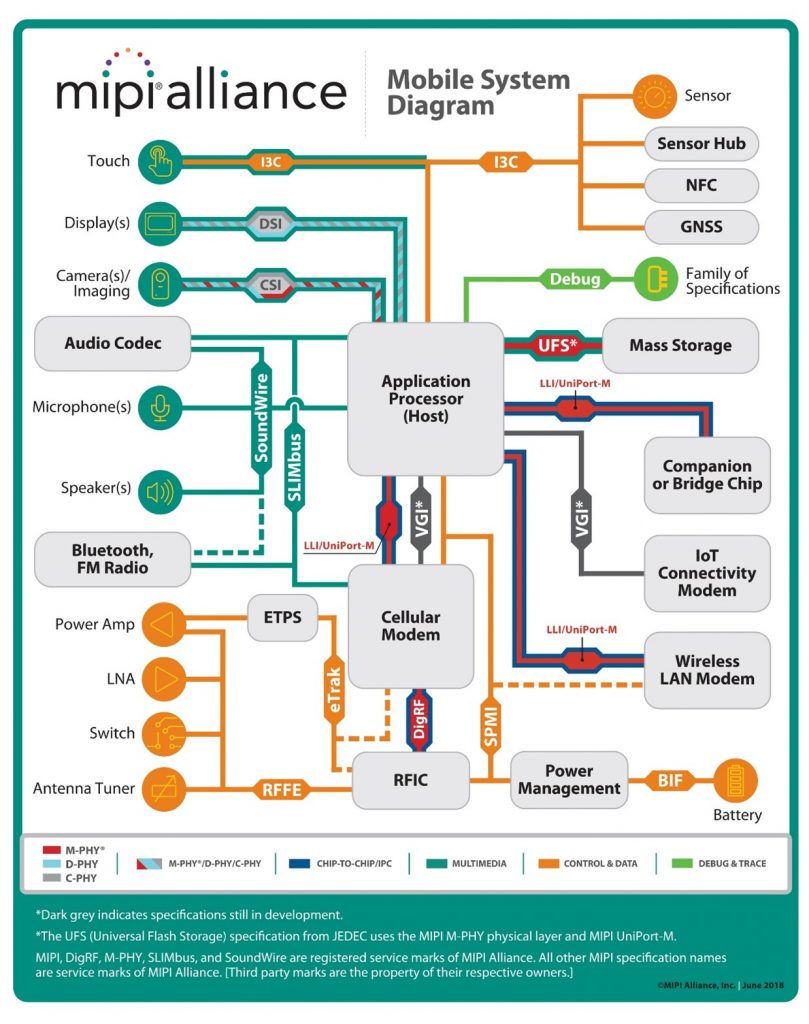

其中每個規範皆經過優化以滿足行動設備所需的嚴格操作條件,包含以下三個特徵:高帶寬性能、低功耗和低電磁干擾(EMI)。下圖為目前MIPI規範的系統架構:

圖 1(https://www.mipi.org/about-us)

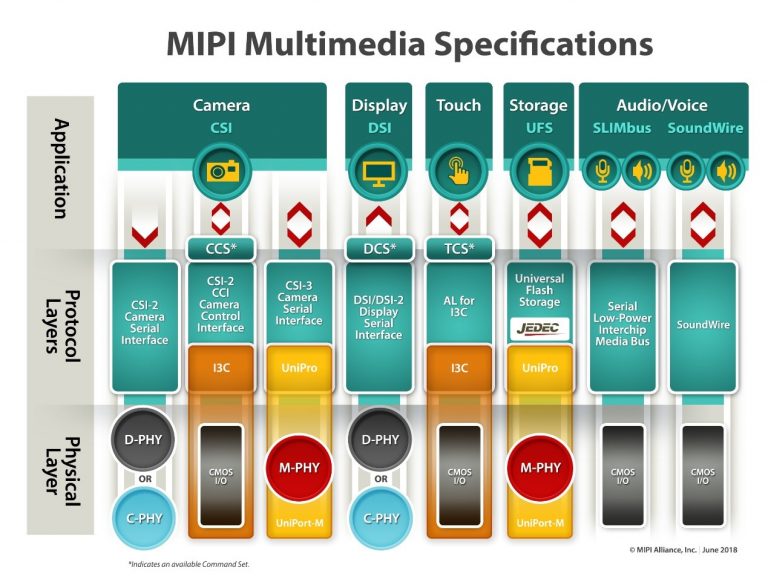

而MIPI規範當中的多媒體(Multimedia)類別,主要分為三個層面(圖2):

- 應用層(Application Layer)

- 協定層(Protocol Layer)

- 實體層(PHY Layer)

其中,與影像傳輸相關的CSI(Camera Serial Interface)為相機串列介面,定義了一個位於攝像模組和處理器之間的高速序列介面;而DSI(Display Serial Interface)則為顯示串列介面,定義了一個位於處理器和顯示模組之間的高速序列介面。由下圖所示,CSI-2以及DSI/DSI-2之實體層包含D-PHY與C-PHY,而本篇文章將著重於前者D-PHY的介紹。

圖 2(https://www.mipi.org/about-us)

MIPI D-PHY 介紹

MIPI D-PHY將百萬像素相機和高解析度顯示器連接到應用處理器,提供靈活、高速、低功耗且低成本的解決方案。同時,由於鏈路收發器的主從關係顯著降低了鏈路的複雜性,適合具有一個主要數據傳輸方向的顯示器和相機案例。

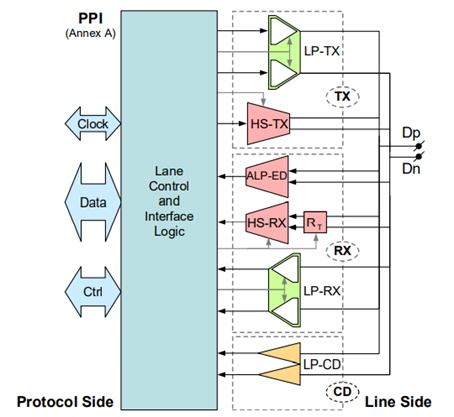

D-PHY的配置包含一條時鐘通道(Clock Lane)以及一條/多條數據通道(Data Lane),其中時鐘通道皆為單向通道,而數據通道可為單向或雙向通道。每條時鐘通道包含Cp、Cn,每條數據通道包含Dp、Dn。

D-PHY當中每條鏈路都有一個主控端(Master)和一個從端(Slave),從主控端至從端為數據傳輸的正向。主控端為時鐘通道提供高速DDR時鐘信號,是主要的數據來源;從端在時鐘通道接收時鐘信號,是主要的數據接收端。在所有情況下時鐘通道與單向數據通道皆保持在正向傳輸,只有雙向數據通道可以反向傳輸,由從端獲取數據。完整的雙向數據通道模組(Universal Lane)示意圖如下:

圖 3(MIPI Alliance Specification for D-PHY, Version 2.0)

MIPI D-PHY 通道收發器

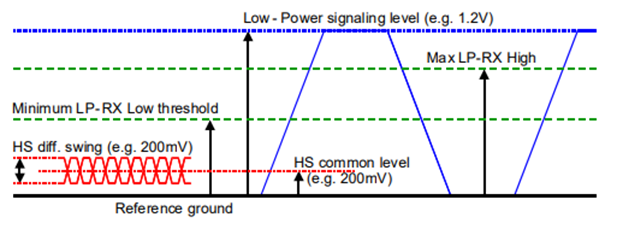

D-PHY通道擁有高速和低功耗兩種收發器,分別為:高速傳送器(HS-TX)、 高速接收器(HS-RX)、低功耗傳送器(LP-TX)、低功耗接收器(LP-RX),因此支援HS(High Speed)和LP(Low Power)兩種傳輸模式。HS模式採用低壓差分信號,雖功耗較大,但是能夠擁有很高的資料傳輸速率(80M~4.5Gbps);LP模式則採用單端信號,雖資料傳輸速率低(<10Mbps),但相對功耗低。HS訊號的電壓範圍為140mV~270mV,而LP訊號的電壓約為1.2V,如下圖所示。此兩種模式的結合使D-PHY能夠在需要時以高速傳輸大量數據,在其餘時間又能夠減少功耗。

圖 4(MIPI Alliance Specification for D-PHY, Version 2.0)

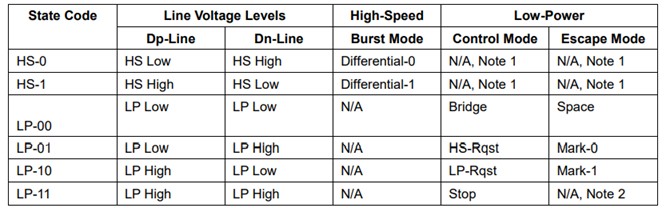

其中高速傳送器以差分方式驅動通道,有兩種通道狀態:Differential-0和Differential-1。低功耗傳送器則以單端方式獨立驅動兩條線路,因此有四種通道狀態:LP-00、LP-01、LP-10和LP11,如下表。LP模式下不同通道狀態的組合可用於控制傳輸訊號進入不同的操作模式,此部分會於後面詳細說明。

表 1(MIPI Alliance Specification for D-PHY, Version 2.0)

MIPI D-PHY 操作模式

D-PHY的操作模式主要共有三種:控制模式(Control Mode)、高速模式(Burst Mode)以及逃逸模式(Escape Mode)。於一般正常操作期間,數據通道將處於控制模式或高速模式。

– 控制模式(Control Mode)

在控制模式之下,數據通道所傳送的訊號為LP訊號,且如上所述有四種通道狀態:LP-00、LP-01、LP-10和LP-11。其中,進入高速模式的順序是:LP-11、LP-01、LP-00,此時數據通道保持高速模式,直到收到停止狀態(LP-11)。而進入逃逸模式的順序是:LP-11、LP-10、LP-00、LP-01、LP- 00。此兩者模式皆須通過控制模式內的請求來進入。

– 高速模式(Burst Mode)

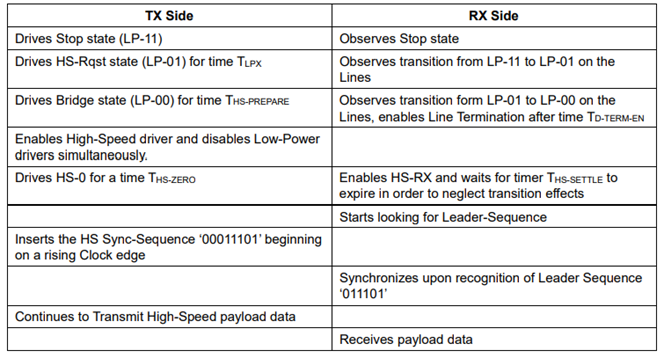

在高速模式之下,高速數據傳輸以突發形式發生,從停止狀態(LP-11)開始和結束。在HS訊號開始傳輸前,數據通道將離開停止狀態,並通過傳輸開始程序(Start-of-Transmission)準備進入高速模式。如表 2,分別描述TX和RX兩側的事件順序。當LP訊號依序走完LP-11、LP-01、LP-00的順序後,RX將會進行Line Termination,TX則會關閉LP訊號驅動程序,並且於同時啟用HS訊號驅動程序。而在數據通道傳輸HS訊號的期間,時鐘通道應處於高速模式,提供 DDR 時鐘。

表2(MIPI Alliance Specification for D-PHY, Version 2.0)

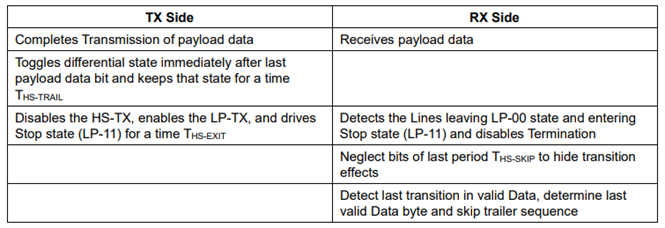

當數據突發結束時,數據通道將通過傳輸結束程序(End-of-Transmission)進入停止狀態,如表3:

表3(MIPI Alliance Specification for D-PHY, Version 2.0)

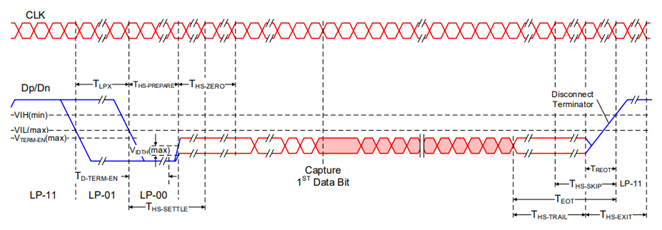

於一般訊號傳輸時,會從控制模式進入高速模式,此時將傳輸HS訊號,當HS訊號傳輸結束,會再從高速模式離開回到控制模式。整個數據突發傳輸期間的事件序列便如同下圖。每條通道的傳輸可以由協議獨立地開始和結束,對於大多數應用程序通道將同步啟動,但由於每個通道傳輸的字節數不等,可能會在不同的時間結束。

圖5(MIPI Alliance Specification for D-PHY, Version 2.0)

– 逃逸模式(Escape Mode)

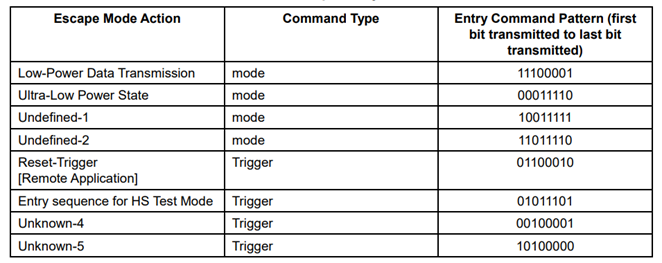

逃逸模式是當數據通道使用低功耗狀態時的特殊操作模式,例如:LPDT(Low-Power Data Transmission)、ULPS(Ultra-Low Power State)、Remote Triggers等。當LP訊號依序走完LP-11、LP-10、LP-00、LP-01、LP- 00,數據通道便進入逃逸模式,此時發送器將發送一個8位元的進入命令來指示請求的動作,如下表。其中,所有未分配的命令都保留用於將來的擴展。停止狀態(LP-11)將用於退出逃逸模式,並且立即返回控制模式。

表4(MIPI Alliance Specification for D-PHY, Version 2.0)

以上即為MIPI D-PHY兩種數據傳輸模式(High Speed、Low Power)以及三種操作模式(控制模式、高速模式、逃逸模式)的相關介紹。

參考文獻

- MIPI Alliance Specification for D-PHY, Version 2.0, 23 November, 2015

作者

GRL 資深測試工程師 藍婉甄 Nicole Lan

擁有四年DP測試經驗,擅長DP、HDR、MIPI等介面測試。GRL技術文章作者及講師。

本文件中規格特性及其說明若有修改恕不另行通知。

發佈日期 2021/10/27 AN-211027-TW